| File Type | Extension | Icon | Description | New Source Wizard Behavior/Tool Launched |

|---|---|---|---|---|

| Block RAM Memory Map (BMM File) | .bmm | Used in PowerPC® and MicroBlaze™ processor designs to describe the organization of Block RAM memory. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. The CPU executable code is automatically inserted in the configuration file during design implementation. | |

| ChipScope Definition and Connection (CDC File) | .cdc | Contains generic information about the trigger and data ports of the ChipScope™ core. | Adds the file to the project. Double-click the CDC file in the Hierarchy pane of the Design panel to run the implementation process and launch the ChipScope Pro Core Inserter. For details, see the ChipScope Pro Tool Debugging Overview. Note The ChipScope Pro tool must be installed for this source type to be available. | |

| Electronic Data Interchange Format (EDIF) | .edn, .edf, .edif, .sedif | Specifies the design netlist in an industry standard file format. | Must be generated by a third-party design entry tool and added to the project. Note You can only add an EDIF file as a top-level module, not as a lower-level module. If you are using hierarchical EDIF files, lower-level EDIF files are automatically processed during the implementation process. | |

| ELF | .elf | Note Only one ELF file is allowed per project. | Must be generated by the Data2MEM command line tool and added to the project. | |

| Embedded Processor | .xmp | Embedded microprocessor project file created with Xilinx Platform Studio. | Launches the Xilinx Platform Studio in which you can define the embedded processor system portion of your design. For details, see the Embedded Development Kit Documentation. | |

| Implementation Constraints File | .ucf | Contains user-specified logical constraints. | Adds the file to the project. Double-click the UCF file in the Hierarchy pane of the Design panel, or double-click a Constraints Entry process in the Processes pane to open the file. You can assign multiple UCFs to the top-level module. For details, see Constraints Entry Methods. | |

| IP (Architecture Wizard) | .xaw | Contains predefined logic functions that configure architecture features or modules. | Launches one of the Xilinx Architecture Wizards in which you can define your IP. For details, see Working with Architecture Wizard IP. | |

| IP (CORE Generator) | .xco | Contains predefined logic functions. | Launches one of the Xilinx IP core customization tools in which you can define your IP. For details, see Working with CORE Generator™ IP. | |

| Memory Definition (MEM File) | .mem | Used to define the contents of memory (RAMB4 and RAMB16). | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. The CPU executable code is automatically inserted in the configuration file during design implementation. | |

| Schematic | .sch | Contains a schematic design. | Opens the schematic file in the Project Navigator Workspace. For details, see the Schematic Overview. | |

| System Generator module | .sgp | Contains Digital Signal Processing (DSP) system module created with System Generator for DSP. | N/A | |

| Targeted device, package, and speed grade | N/A | Shows the targeted device, package, and speed grade. | N/A | |

| Undefined | N/A | Contains an instantiated module that has not been added to the ISE project but is referenced by a source file in the ISE project. | N/A | |

| User Document | Multiple file types | Contains user information that is not implemented with the project, for example, supporting documentation. | N/A | |

| Verilog Module | .v | Contains Verilog design code. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| Verilog Test Fixture | .v | Defines the stimulus to the ports of an HDL file. | Prompts you to associate the file with a Verilog source module and then opens a skeleton test bench file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| VHDL Library | N/A | Contains a collection of VHDL packages. | Adds a new directory to the vhdl library directory in the Libraries panel. | |

| VHDL Module | .vhd | Contains VHDL design code. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| VHDL Package | .vhd | Contains definitions, macros, sub-routines, supplemental types, subtypes, constants, functions, and other files. | Opens the file in the text editor you specify in the Editors page of the Preferences dialog box. | |

| VHDL Test Bench | .vhd | Defines the stimulus to the ports of an HDL file. | Prompts you to associate the file with a VHDL source and then opens a skeleton test bench file in the text editor you specify in the Editors page of the Preferences dialog box. |

There is a lot of different schematic software on the market. Most is designed for a special application like entry for simulation, schematic supported layout generation or just for documentation. Carnival of rust mp3 320kbps. Some software is limited to PCB or to IC circuits. The SchematicEditor does not have these limitations and combines all listed applications. Futhermore is can be used for a Parametric Mask Layout together with the LayoutEditor. This makes it a versatile tool for all types of applications -- IC, MEMS, PCB, Microwave, . Prepare to be impressed!

Adobe Systems Incorporated created the EDIF Implementation Netlist File (EDN) file for the Adobe Acrobat DC software series. Trane ahu manual. Annoymous user data statistics infer that EDN files are most popular in United States and with those using Windows 10 devices.

Designing Schematics

A comfortable editing with a intuitive user interface is important for a SchematicEditor as well. The design of the user interface in the SchematicEditor is similar to the LayoutEditor. So also here an outstanding usability is achieved, plus a big synergy effect, if you use both LayoutEditor and SchematicEditor. |

- EDIF is probably the most famous of the net-based netlists. Hierarchy edit In large designs, it is a common practice to split the design into pieces, each piece becoming a 'definition' which can be used as instances in the design.

- EDIF Input File (.edf) Definition An EDIF version 2 0 0 netlist file (with the extension (.edf), generated by any standard EDIF netlist writer. The Quartus® Prime Standard Edition software also supports EDIF Input files with the extensions (.edif) or (.edn).

Supported File Formats

Versatility is not just a question of available feature, but in particular a question of cooperation with other software. In order to achieve the maximum possible here, a large number of file formats for schematics, netlists and libraries are supported. Thus, for example a schematic created with LTspice can be loaded into the SchematicEditor directly. (see screen shot on the right). |

Besides its own format for storing schematics and libraries these file formats are supported: Sea ray hull id decoder. |

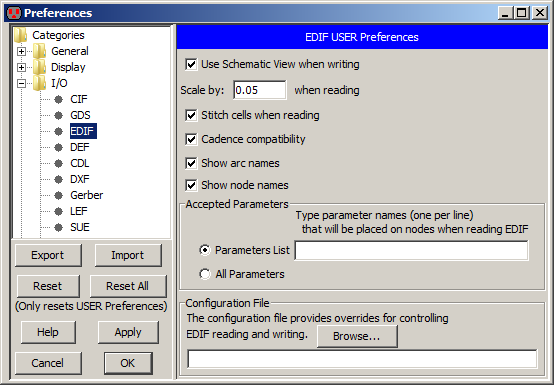

OpenAccess, EDIF, Qucs, LTSpice, SVG, JPG, . |

Additional any text based netlist format can be created. Just a simple setup is required to define a further format. Also any schematic can be converted to the layout window. So it can be exported to a wide range of graphic formats for documentation. |

Simulation

Edif Netlist

A common design flow is to design a circuit, simulate and optimize it, create a layout and verify it. To follow this flow the simulation part in the LayoutEditor/SchematicEditor is missing. But this is not a problem as the SchematicEditor works together with many external simulators. So the circuit can be simulated with more than one simulator and the simulation results can be compared. The simulation can be triggered from inside the SchematicEditor. Doing so a netlist will be generated, the simulator be called and after completion a wave form viewer can be called by the SchematicEditor. The hole sequence is controlled by a macro and can simple be adjusted by anyone. Complete and tested macros are shipped for some common simulators like HSPIE, LTspice, ngspice or Qucs and need no more (or minimal) setup to use. |

Schematic Driven Layout

Creating a layout from a schematic is a widespread task where EDA software is used. The SchematicEditor is linked with the LayoutEditor, which enables a comfortable schematic driven layout. Place/choose a device in the schematic window and simple move the mouse to the layout window to get the corresponding device design. Select a node in one window and it is displayed in the other window. These features support the design without restricting a free custom design. |

Edif Netlist File Format Pdf

Layout Versus Schematic

Airmail vs spark for mac review. Validating a design is normally one of the last steps. The combination LayoutEditor with SchematicEditor supports this. A netlist can be extracted for a build-in or external layout versus schematic (lvs).The build-in LVS make it very simple to follow up an error. |

Documentation and more

There is much more to say about SchematicEditor features. Dua for traveling in arabic. Please have a look into the documentation especially on the list of all Schematic Features. Or just try it out and be impressed! |

Still anything missing? No problem! New ideas to improve the SchematicEditor are always welcome! Please leave a note or contact: [email protected] |

License Store | Download | Manual | Support | Impressum | Data Privacy Policy

Schematic (last edited 2014-09-12 16:36:15 by J端rgenThies)